Project templates: the new launch checklists

Every aerospace mission begins with a checklist; fuel, pressure, comms, weather. Future hardware teams will start projects the same way. AI-powered templates for power tables, BOM structures, and review frameworks ensure that no one starts from scratch. Like automotive engineers who rely on proven crash-test protocols, electrical engineers will rely on these standardized starting points.

Having a standard power table template means your team isn’t reinventing the same calculations every project.

Aligning to the roadmap: headlights on the road ahead

In cars, headlights don’t just illuminate what’s in front; they let you anticipate the curves ahead. Future AI tools will align individual design decisions to program-level roadmaps. If a critical block is falling behind, or a resource conflict is building, leadership will see it before it derails the project.

You want to see when board-level delays put the product launch at risk, not after the fact.

Smarter design file interactions: the robotic co-pilot

On modern assembly lines, robots don’t replace workers; they handle the repetitive, high-precision tasks. In hardware design, AI will play a similar role. Engineers will prompt AI to suggest safe edits, generate block-level circuits, or produce review checklists. These models will take important context, like component libraries, approved vendors, and preferred circuits into account. It’s like having a robotic co-pilot: steady hands on the yoke while the pilot charts the course.

Auto-generating review checklists from schematics saves you hours and catch errors earlier.

Adding organizational context: the factory memory

Industrial plants don’t just rely on the workers on shift; they build institutional knowledge into the system itself. The future of hardware engineering will look similar. Companies will maintain “EE databases” where parts, footprints, test data, and lessons learned become machine-readable. AI can pull context from this history, preventing the same mistakes from repeating.

You need every failed footprint and test result logged so the next board doesn’t repeat the same mistake.

Translation layers for ECAD data: the universal adapter

Think of international travel without power adapters; every country’s outlets are different. That’s how hardware feels today, with ECAD data locked in silos. Translation layers will act as universal adapters, mapping ECAD to firmware registers, server routines, and mechanical interfaces. Consumer electronics already depend on such seamless integration; hardware engineering will soon expect the same.

Mapping schematic pins directly to firmware registers eliminates many handoff transfers.

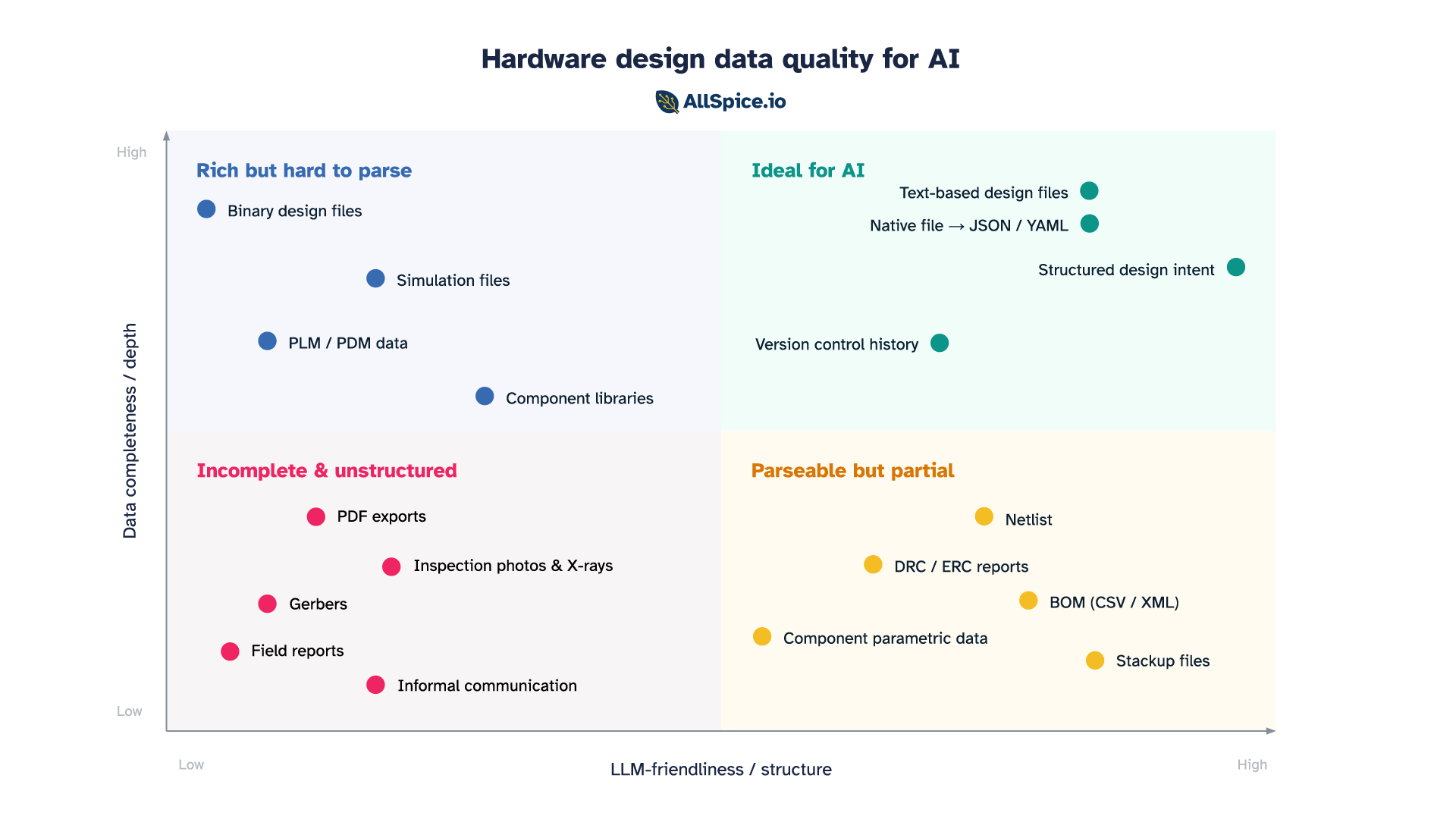

Domain-specific AI models and knowledge bases: the aerospace-grade instruments

You wouldn’t fly a rocket with consumer-grade GPS. Aerospace demands specialized instruments tuned for precision and reliability. In the same way, hardware teams will rely on AI models trained on domain-specific ECAD and organizational knowledge, not just general-purpose chatbots.

Generic AI can’t read a multi-page schematic, but a model trained on ECAD can flag risks in minutes.

Automation-first workflows: the pit crew model

In motorsports, pit crews win races by executing routine tasks faster than any individual could. Hardware engineering will adopt a similar “function-call” approach: instead of manual reviews, engineers will invoke automated checks “run thermal risk analysis,” “validate footprint consistency”, with AI executing instantly.

Running a thermal check like a function call, means more time designing and less time troubleshooting.

Smarter connections to simulation and CM systems: the supply chain autopilot

Consumer devices today are built on global supply chains coordinated by software. Future hardware workflows will integrate AI with simulation and contract manufacturer (CM) systems. Simulation results; thermal, SI, PI, will automatically feed into design reviews. CM handoffs will be pre-validated before files leave engineering. It’s supply chain autopilot, ensuring smooth landings instead of turbulence.

Having simulation data flow straight into CM deliverables cuts time out of every release cycle.

Closing: don’t blink

Aerospace, automotive, industrial, consumer, the same story plays out across industries: those who adapt thrive, those who hesitate miss the window. Hardware engineering is no different. The future isn’t about AI replacing engineers. It’s about engineers who know how to harness new levers; standardization, automation, and domain-specific intelligence, so they can launch faster, build safer, and deliver more reliably.

Don’t blink. The future is already on the runway.

📣 Want to see what AI-driven hardware design actually looks like in practice?

If this chapter sparked ideas about where hardware design is heading, don’t miss our upcoming live webinar:

🔧 How to use agentic AI for better hardware design reviews

A practical, engineer-focused deep dive into what AI can really do for modern hardware teams.

You'll learn:

- ⚠️ The real risks in hardware design and how AI helps teams address them

- 📘 A case study of how engineering teams are adopting AI today

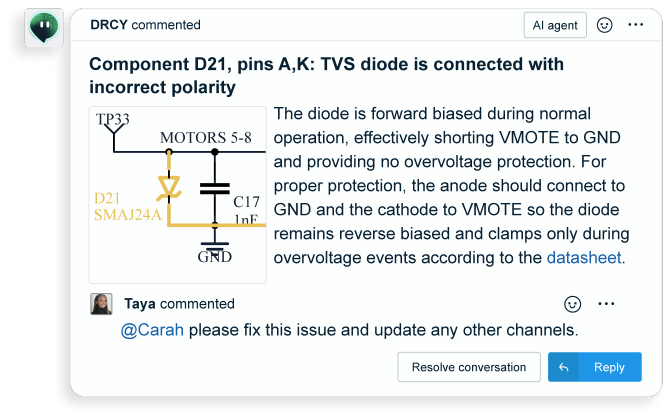

- 👁️ What an AI design review agent actually looks like in action

- 🔌 A live walkthrough of DRCY, AllSpice’s agentic AI for hardware

- ✨ Real outcomes teams are seeing in production design cycles

- 🧠 How AI compares with deterministic intelligence (CI/CD, rule checks)

- 📝 How to get new engineering tools approved internally

- 🔐 Security and IT implications when adopting AI

- ❓ Live Q&A with our engineering experts

This session is tailored for roles like hardware engineering managers, individual-contributor EEs, VPs of hardware, and engineering efficiency leaders, anyone looking to reduce risk, accelerate design cycles, and modernize their review workflows.

Come join us!

Further reading

Generative AI meets CAD: enhancing engineering design to manufacturing processes with large language models

(Springer) Discusses how combining LLMs with engineering templates and pin mappings allows semi-automated, human-in-the-loop workflows in CAD.

https://link.springer.com/article/10.1007/s00170-025-15830-2

ChipNeMo: Domain-Adapted LLMs for Chip Design

Describes domain adaptation techniques for language models focused on chip design, which aligns

with the idea of domain-specific AI models & knowledge bases.

https://arxiv.org/abs/2311.00176

Hardware Design and Verification with Large Language Models: A Review

(MDPI) Surveys use of LLMs in hardware design & verification, helps ground the “future” claims with what’s already emerging.

https://www.mdpi.com/2079-9292/14/1/120

How generative AI puts the magic back in hardware design

(EDN) Talks about generative AI augmenting hardware design workflows, automating repetitive tasks, etc. A good source for “robotic co-pilot” or “automation-first workflows.”

https://www.edn.com/how-generative-ai-puts-the-magic-back-in-hardware-design/

Building the next generation of hardware: Why AI-powered engineering

tools matter (ScaleVP) Offers perspective on how AI tools are already transforming engineering tools, highlighting that what seems futuristic is accelerating into now.