AllSpice’s AI principles

Our approach to AI follows three principles. First, AI should reduce risk, not add it. That means focusing on advisory tasks where AI assists engineers without taking control away. Second, AI should integrate into existing workflows instead of creating new silos. Third, AI should remain pragmatic: it can call checks, parse data, and flag risks, but it doesn’t replace simulation or CAD software. Parsing schematic and layout files is central here, by breaking designs into normalized, structured elements and producing files like BOMs automatically, AllSpice ensures AI can operate on data, not static images.

Where general AI struggles

General-purpose AI can already help with tasks like drafting test scaffolds, validating attributes against datasheets, and summarizing design diffs. But on engineering artifacts, it quickly runs into limits. Parsing schematic PDFs often produces inconsistent results. Multipage designs break context. Large binary layout files overwhelm standard models. Symbols and footprints often look interchangeable to generic AI, which leads to subtle but costly errors. AllSpice solves this by ingesting schematic, layout, symbol, and footprint data directly from source formats, and generating structured outputs like BOMs or XY files that give AI the clarity it needs.

Why specialized approaches matter

AllSpice addresses these gaps by combining retrieval-augmented generation (RAG) with ECAD-aware models. We provide review instructions in our AllSpice EE Knowledge Base. Instead of feeding entire schematic PDFs into a model, AllSpice breaks designs down into nets, components, footprints, and symbols.

These structured elements are stored and indexed so AI can retrieve the right context at the right time. For example, when reviewing a power net, AllSpice’s parser knows which symbol connects where, which footprint implements it, how it maps into the PCB layout, and what BOM entry it produces. This prevents the common blind spots that generic AI falls into.

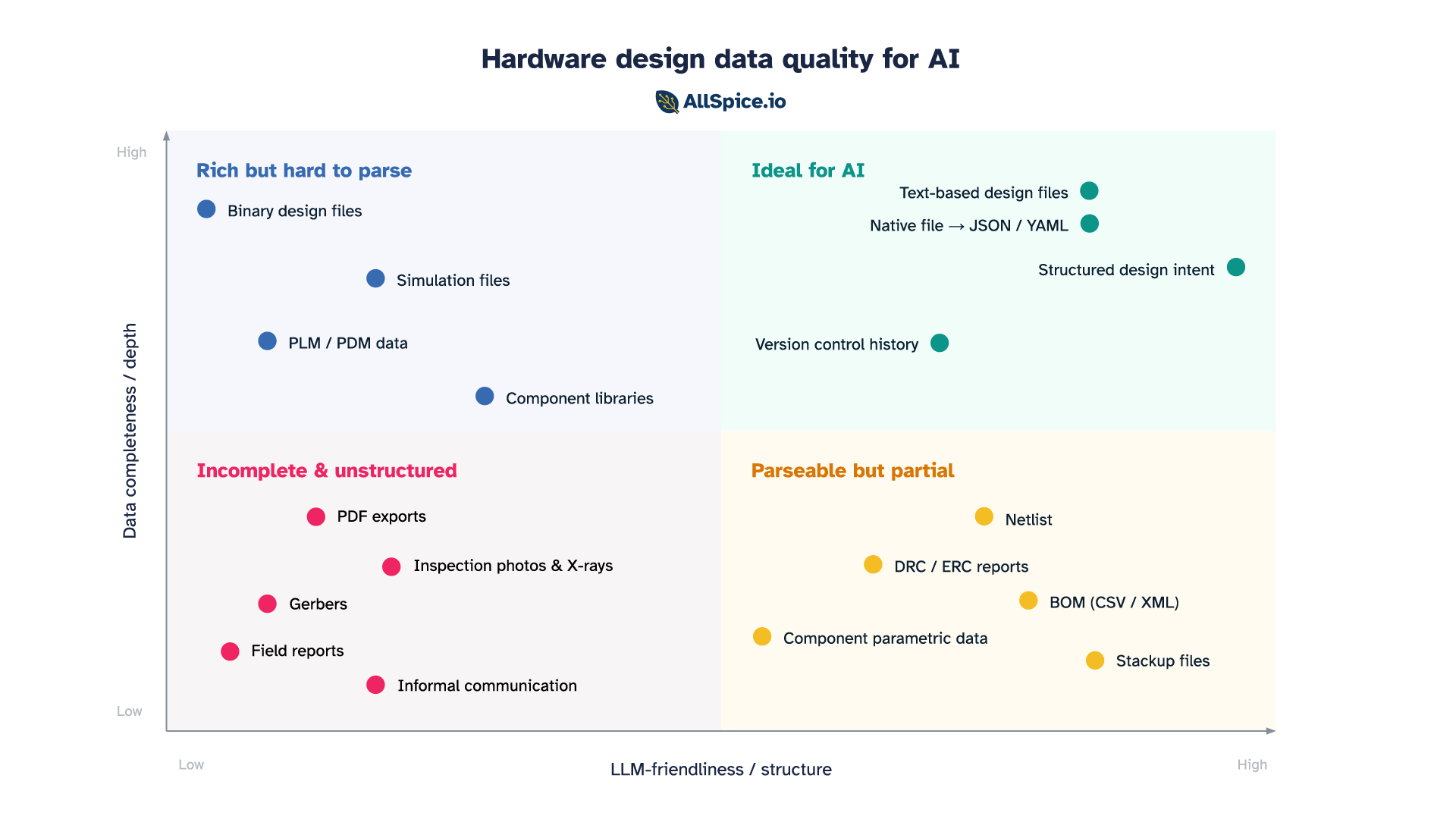

The data challenge

Hardware data comes in many forms. Some formats, like KiCad or JSON, are structured and easier to process. Others; proprietary binaries, encrypted design files, or scanned PDFs, make direct AI use nearly impossible. AllSpice solves this by normalizing these inputs. Schematics, PCB layouts, footprints, and symbols are parsed into structured datasets, and files like BOMs, drill maps, or placement data are generated automatically. This structured foundation enables analysis across artifacts like Gerbers and manufacturing packages. Without parsing and normalization, even the best AI model is working blind.

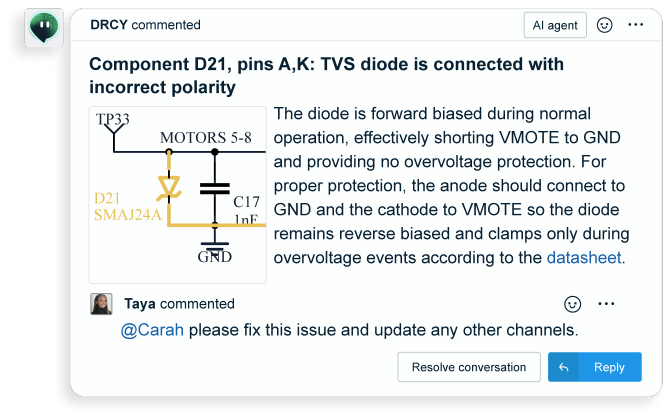

Meet DRCY: AI-powered design reviews in AllSpice

AllSpice’s first AI application is DRCY, an AI review agent that works like another reviewer on your team. Engineers can tag DRCY directly in a pull request, and it will run a structured design review on the submitted files. Instead of broad commentary, DRCY produces targeted feedback grounded in component datasheets and design context.

- Connection checks: Builds a table of critical components, pin designators, and net connections, highlighting mismatches and missing references.

- Datasheet-aware analysis: Cross-references components against their datasheets to flag incorrect pin mappings or usage errors.

- Version comparisons: Identifies differences between design revisions and explains the impact of those changes.

- New file reviews: Beyond diffs, DRCY can review netlists and schematics directly, surfacing issues before the layout stage. DRCY can be configured to run against internal LLMs to meet compliance and security needs.

What DRCY does *not* do is just as important. It doesn’t generate freeform, real-time commentary, perform board-level PCB design reviews, or replace engineers in the comment threads. Its role is to augment reviews, not automate them away.

By embedding DRCY into the same Design Review workflow engineers already use, AllSpice ensures AI review is frictionless, structured, and always grounded in real design data.

These capabilities don’t replace engineer judgment, they accelerate it, surfacing issues before they escape into late-stage validation.

Closing: don’t blink

Aerospace, automotive, industrial, consumer, the same story plays out across industries: those who adapt thrive, those who hesitate miss the window. Hardware engineering is no different. The future isn’t about AI replacing engineers.

It’s about engineers who know how to harness new levers; standardization, automation, and domain-specific intelligence, so they can launch faster, build safer, and deliver more reliably.

Don’t blink. The future is already on the runway.

Further reading

- Generative AI meets CAD: enhancing engineering design. Discusses how combining LLMs with engineering templates and pin mappings allows semi-automated, human-in-the-loop workflows in CAD. https://link.springer.com/article/10.1007/s00170-025-15830-2

- ChipNeMo: Domain-Adapted LLMs for Chip Design. Describes domain adaptation techniques for language models focused on chip design, which aligns with the idea of domain-specific AI models & knowledge bases. https://arxiv.org/abs/2311.00176

- Hardware Design and Verification with Large Language Models: A Review (MDPI). Surveys use of LLMs in hardware design & verification, helps ground the “future” claims with what’s already emerging. https://www.mdpi.com/2079-9292/14/1/12

- How generative AI puts the magic back in hardware design (EDN).Talks about generative AI augmenting hardware design workflows, automating repetitive tasks, etc. A good source for “robotic co-pilot” or “automation-first workflows.” https://www.edn.com/how-generative-ai-puts-the-magic-back-in-hardware-design/

- Building the next generation of hardware: Why AI-powered engineering tools matter (ScaleVP). Offers perspective on how AI tools are already transforming engineering tools, highlighting that what seems futuristic is accelerating into now. https://www.scalevp.com/insights/building-the-next-generation-of-hardware-why-ai-powered-engineering-tools-matter/